UNIVERSITÉ LIBRE DE BRUXELLES Faculté des Sciences Département d'Informatique

# Provably Correct Code Generation of Real-Time Controllers

Mémoire présenté en vue de l'obtention du grade de Licencié en Informatique

> Nicolas MAQUET Année académique 2005–2006

# Remerciements

Ce sujet de mémoire m'a été proposé par M. Jean-François Raskin. Je tiens à le remercier pour son aide apportée tout au long de la réalisation de ce travail. Son enthousiasme pour la recherche et son intransigeance technique sont pour moi des exemples.

Je tiens également à remercier M. Laurent Doyen et M. Martin De Wulf, et tout particulièrement ce dernier pour avoir relu et commenté de nombreuses versions de ce travail, et pour avoir répondu avec bonne humeur à mes myriades de questions.

Je remercie tout le corps académique du Département d'Informatique, pour leur travail de tous les jours à la réalisation d'un enseignement scientifique de qualité.

Un grand merci à tous mes amis, pour leur chaleureux soutien dans les moments difficiles et leur présence de tous les jours. Un remerciement tout particulier à Thierri de Vos pour son intérêt enthousiaste à mes travaux, et pour avoir accepté de m'aider à la réalisation d'un chapitre de ce mémoire mais qui n'a malheureusement pas abouti (il s'agissait d'une étude de cas supplémentaire impliquant des automates hybrides). Ton travail ne restera pas vain, ce n'est que partie remise!

Enfin, je tiens à témoigner ma gratitude envers toute ma famille pour leur amour et leur soutien tout au long de mes études. Je ne peux pas vous remercier tous personnellement ici, mais je ne peux m'empêcher de citer ceux et celles que je vois et qui me soutiennent quotidiennement (et qui donc, en particulier, ont du me supporter jour après jour pendant la rédaction de cet ouvrage ...) : Maman, Chloé, Roland, Martine, Maxime, Philippe, Catherine, Étienne, et Amandine. Merci!

À mon frère, Laurent Maquet À mon père, Philippe Maquet

# Contents

| 1 | Inti                 | roduction                                           | 2 |

|---|----------------------|-----------------------------------------------------|---|

|   | 1.1                  | Formal Methods for Software Verification            | 2 |

|   |                      | 1.1.1 Bottom-Up Approach                            | 2 |

|   |                      |                                                     | 3 |

|   | 1.2                  | Provably Correct Real-Time Controllers              | 3 |

|   | 1.3                  | ·                                                   | 4 |

|   | 1.4                  | Modeling Environments With Timed or                 |   |

|   |                      | <u> </u>                                            | 5 |

|   | 1.5                  |                                                     | 6 |

|   | 1.6                  | 0 01                                                | 7 |

|   | 1.7                  | v                                                   | 8 |

|   | 1.8                  | ı v                                                 | 8 |

|   | 1.9                  | - •                                                 | 9 |

|   |                      |                                                     |   |

| 2 | $\operatorname{Tin}$ | ned Automata 11                                     |   |

|   | 2.1                  | Syntax of Timed Automata                            | 1 |

|   | 2.2                  | Classical Semantics of Timed Automata               | 5 |

|   | 2.3                  | Timed Systems Analysis                              | 9 |

|   | 2.4                  | Timed Automata in the Literature                    | 1 |

| 3 | Imp                  | olementability of Timed Controllers 22              | 2 |

|   | 3.1                  | Overview of the Almost ASAP Approach                | 4 |

|   | 3.2                  | Simulation and Controller Refinement                | 4 |

|   | 3.3                  | ELASTIC Controllers and ASAP Semantics              | 6 |

|   | 3.4                  | Almost ASAP Semantics                               | 6 |

|   | 3.5                  | Almost ASAP Semantics Analysis                      | 2 |

| 4 | Imr                  | plementation Semantics 33                           | 3 |

| - | 4.1                  | Program Semantics                                   |   |

|   | •                    | 4.1.1 Formalization of the Program Semantics        |   |

|   |                      | 4.1.2 Comments on the Program Semantics             |   |

|   |                      | 4.1.3 AASAP Simulability of the Program Semantics 3 |   |

|   |                      | 4 1 4 Implementability of the Program Semantics 39  |   |

|   | 7.5          | Execution of the Generated Code                     | 84        |

|---|--------------|-----------------------------------------------------|-----------|

|   |              | 7.4.5 Assigning the RT Semantics Parameters         | 84        |

|   |              | 7.4.4 Receiver Decoration                           | 82        |

|   |              | 7.4.3 Receiver Specification                        | 82        |

|   |              | 7.4.2 Sender Decoration                             | 80        |

|   |              | 7.4.1 Sender Specification                          | 80        |

|   |              | using Spectre                                       | 80        |

|   | 7.4          | Systematic Implementation of the PACP               |           |

|   | 7.3          | Verification Results                                | 79        |

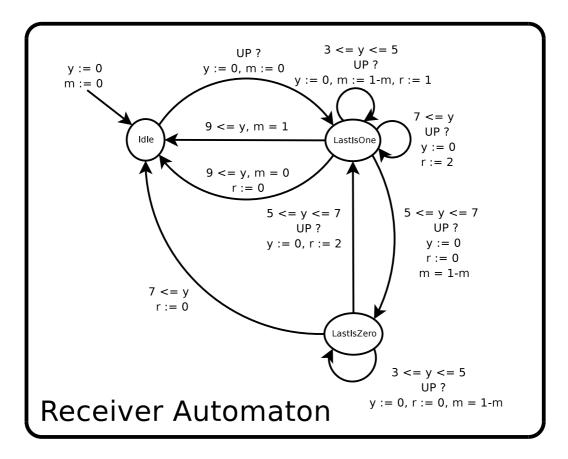

|   |              | 7.2.2 Receiver Automaton                            | 78        |

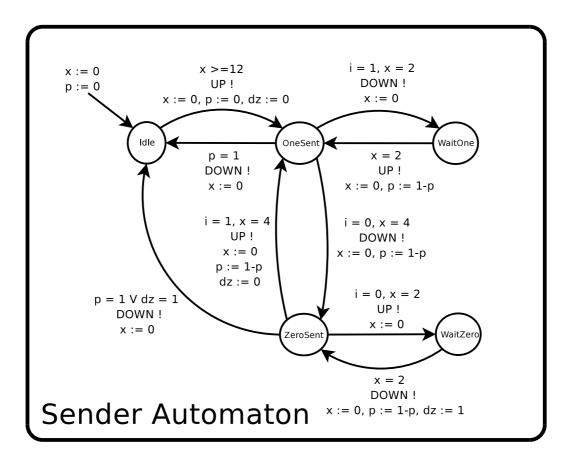

|   | 1.4          | 7.2.1 Sender Automaton                              | 77        |

|   | $7.1 \\ 7.2$ | Modeling the PACP with Timed Automata               | 76        |

| • | 7.1          | Description of the PACP                             | 76        |

| 7 | Cas          | e Study : Philips Audio Control Protocol            | 75        |

|   | 6.4          | Implementation of Spectre                           | 74        |

|   | 6.3          | Use of the Spectre Decoration Language              | 73        |

|   |              | 6.2.2 Correctness of the Generated Code             | 72        |

|   |              | 6.2.1 Architecture of the Generated Code            | 66        |

|   | 6.2          | Code Generation                                     | 66        |

|   |              | 6.1.2 Decoration Section                            | 61        |

|   | 0.1          | 6.1.1 Specification Section                         | 59<br>59  |

| U | 6.1          | Input Language                                      | <b>59</b> |

| 6 | Cod          | le Generation of Real-Time Controllers              | 59        |

|   | 5.3          | The RTAI Scheduler                                  | 57        |

|   |              | 5.2.2 Task-Management Routines                      | 56        |

|   |              | 5.2.1 Timer Routines                                | 54        |

|   | 5.2          | RTAI Service Routines                               | 54        |

|   | 5.1          | Architecture of RTAI                                | 53        |

| 5 | RTA          | AI : GNU/LINUX Made RT Capable                      | 53        |

|   |              | 4.2.5 Benefits of the Real-Time Semantics           | 52        |

|   |              | 4.2.4 Implementability of the Real-Time Semantics   | 51        |

|   |              | 4.2.3 AASAP Simulability of the Real-Time Semantics | 44        |

|   |              | 4.2.2 Formalization of the Real-Time Semantics      | 42        |

|   |              | 4.2.1 Overview of the Real-Time Semantics           | 41        |

|   | 4.2          | Real-Time Semantics                                 | 40        |

|   |              | 4.1.5 Limitations of the Program Semantics          | 38        |

| A Spe | CTRE Grammar                   | 91 |

|-------|--------------------------------|----|

| A.1   | Typographical Conventions Used | 91 |

| A.2   | Grammar                        | 91 |

# Chapter 1

# Introduction

This work studies a methodology for creating provably correct real-time software controllers. A real-time software is a program for which the correctness depends not only on the soundness of its outputs, but also on the time at which those outputs are produced. For instance, a nuclear power-plant emergency shutdown sequence might involve numerous steps such as opening valves, raising robotic arms, triggering sound alerts, etc. Each of those steps must be accomplished in a timely fashion in order to prevent a catastrophe. When the possible damage caused by software failure reaches a certain point, it is more and more considered necessary to have some kind of formal assurance that the control software will always operate as required, that is by keeping the controlled environment in a safe state (the plant has not exploded, the aircraft has not crashed, etc.). To obtain this formal assurance, we need a way of reasoning on control software such that a proof of correctness can be constructed. This is done by (1) constructing a formal model  $\mathcal{M}$  of the system (including environment and control software), (2) by specifying a formal property  $\psi$  that the model needs to satisfy, and (3) by proving that  $\mathcal{M} \models \psi$ . When such a proof can be obtained, we say that the control software is provably correct.

## 1.1 Formal Methods for Software Verification

Several formal methods for creating provably correct software have been studied in computer science, each having their own particularities. These methods can be classified in two distinct categories, which we introduce in turn.

# 1.1.1 Bottom-Up Approach

One way of reasoning about software that yields correctness proofs works by proceeding *bottom-up*. Based on informal specifications, a software solution is created, using standard software design techniques. After this first step, the

control software and its environment are then *abstracted*, to provide a formal model. Great care has to be put into this abstraction phase, to make sure that the model is a sound *over-approximation* of the real system.

The notion of over-approximation is a key concept in software verification. In short, a formal model correctly over-approximates a real-world system if we have that every property which can be proven true on the model will also be true for the real system. This is done by ensuring that every possible behavior of the real system is *included* in the set of behaviors that the model contains. The model can contain *more* behaviors however, hence the term *over-approximation*.

Once the formal model has been created, it is possible to reason on that model in a formal way, in order to obtain formal assurance that the real system is indeed correct (i.e. it satisfies some formal specification).

## 1.1.2 Top-Down Approach

Another approach to software verification (and the one we will use in this study) works the other way around. Using the informal specifications of the system to implement, a model is created before the beginning of the implementation process. The same care has to be put into the model design than in the former approach, in order to reason on a sound over-approximation of the target system. This approach however, has one considerable advantage: after having verified that the model is correct, it is possible to construct the implementation of the software in a systematic way. This of course requires that the model be designed in such a way that a systematic implementation is possible. Another considerable advantage of the top-down approach is that it can detect design flaws before the implementation process. If severe errors are found after the implementation has been created, part of the programming effort will have been wasted.

## 1.2 Provably Correct Real-Time Controllers

In this work, we will use a top-down verification approach and apply it in the context of real-time embedded controllers. In this study, a *controller* is a real-time software interacting with an environment, and which has the responsibility of keeping its environment in a safe state (or set of states). Such controllers are often *embedded* physically in their environments, as for instance the ABS which is found in cars, or the auto-pilot software aboard airplanes. These embedded applications are often found in safety-critical environments, justifying the need for formal verification.

The verification process that we will use to verify software controllers will focus on the soundness of its *output commands*. We will not care so much about the secondary computations that the controller must make to take decisions,

but rather focus on verifying that the controller is able to issue the appropriate commands at the right time, in all situations.

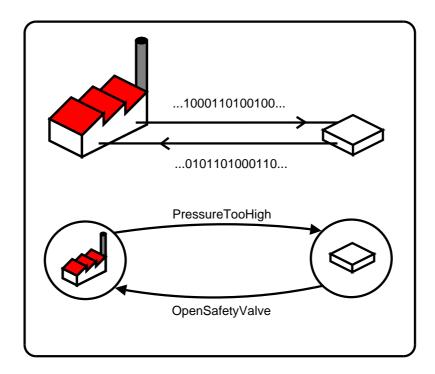

For example, consider a controller interacting with a valve, which needs to be operated to regulate the air-pressure of a tank. The software controller is aware of the current air-pressure by using an input-sensor and is linked to the valve by an output port. The valve control chip periodically reads an integer value on its input port and changes the valve opening angle accordingly, in realtime. In this situation, the control software operates by monitoring an integer input value and changing an integer output value accordingly. Our verification methodology will not manipulate these values directly, but rather abstract them with events. In this case, the output command could be abstracted by a single ChangeValveAperture event, and our verification process will be able to verify that it is issued by the controller appropriately. The rationale behind this abstraction is that (1) it greatly simplifies the design of the controllers and (2) that once it has been proven that the right command is always emitted at the right time, it is always possible to prove that the actual contents of that command is also appropriate, if need be. This latter verification would need other techniques which are beyond the scope of this work, so we will not discuss them further. The abstraction of controller-environment communication is illustrated at figure 1.1.

By abstracting the inputs and outputs of our software controllers with events, it is possible to design and analyze them in a natural way by using language theory. Hence, we will model the software control-logic with automata. Likewise, we will construct models for the environments using automata, and study the system as a whole, using the *composition* of the controller and environment automata.

# 1.3 Modeling Real-Time Controllers with Timed Automata

Since we need to design and verify control logics with real-time requirements, finite-state machines (regular languages) do not suffice in our context. We will need a more powerful computation model to analyze real-time software controllers, namely the *timed automaton*.

Timed automata have been introduced in [AD94], as an extension to regular automata incorporating the notion of time, and have been widely adopted in the research community as a tool for modeling real-time systems. A timed automaton is a finite-state machine augmented with a finite number of *clocks*. These clocks are real-valued variables which are used to count time and thus have a first derivative equal to one. They are used to restrict the possible behaviors of the automaton, by adding timing constraints to its nodes and edges. For example it is possible to express behaviors such that "stay in that location while clock x is

Figure 1.1: Abstraction of real-world communications using events. The top part of the figure represents the real-time data exchange between the controller and its environment, as it really occurs. For our verification purposes, we will study these communications using abstract events, as shown on the bottom part of the figure.

smaller than 3" or "take that edge as soon as clock y is equal to 2", etc. Timed automata are defined formally in the next chapter.

The popularity of timed automata is such that a number of model-checking tools exist to facilitate their analysis. The most notable ones include UPPAAL [BLL<sup>+</sup>98] and KRONOS [DOTY95].

# 1.4 Modeling Environments With Timed or Hybrid Automata

Our verification approach is applicable to environments modeled with timed or hybrid automata.

Hybrid automata [Hen96] are more sophisticated computation models than timed automata, as they allow for more complex continuous behaviors. A hybrid automaton can not only model time, but also any continuous dynamics such as temperature, voltage, height, pressure, etc. Like the timed automaton, the hybrid automaton is equipped with a finite number of variables, but their first derivative is not necessarily equal to one; in fact, it does not even need to be constant, as

hybrid automata define their continuous dynamics with differential equations.

The tank environment of the previous section for example, could be modeled elegantly with a hybrid automaton. It would have a variable representing the pressure of the tank, with each discrete location enforcing a particular pressure dynamics (indicating how fast the pressure rises when the valve is closed, for instance). With an environment modeled this way, it is possible to verify formally that the pressure variable will never reach some critical threshold for example.

Unlike with timed automata, the analysis of hybrid automata turns out to be undecidable in the general case<sup>1</sup>. This is immediate, because we do not know how to solve differential equations in general. To work around this undecidability, several subclasses of hybrid automata have been studied, most notably the rectangular hybrid automaton. The study of these subclasses has made it possible to analyze hybrid automata with the help of automated tools. These tools include for example HYTECH [HHW97] and PHAVER [Fre05].

In this work we will restrict ourselves to the use of timed automata. However, our methodology is completely applicable to environments modeled with hybrid automata.

## 1.5 Synchrony Hypothesis

Many approaches to the software verification problem use what is usually referred to as the *synchrony hypothesis*. When making that hypothesis we assume that the hardware on which our software controller will run is *perfect* in the following sense:

- 1. The synchrony hypothesis assumes an infinitely fast hardware. This implies that (1) any computation can be done in zero time units, and (2) that the controller can read input data and emit output commands instantaneously.

- 2. It also assumes that clock rounding errors never happen; this is essentially the same as requiring hardware clocks of infinite precision.

- 3. Finally, it assumes that the hardware clocks do not drift. A drifting clock is a digital clock which sometimes "looses" a tick, yielding inaccurate time readings. No real-world clock has a drift of zero, even the most sophisticated atomic clocks do drift (albeit *very* slowly).

The reason why such an unrealistic hypothesis is used is that (1) it *greatly* simplifies the design and analysis of software systems and (2) that in many situations the execution times and rounding errors are just too small compared to the scale of the environment. Indeed, if every delay or time lapse is of several orders

$<sup>^{1}\</sup>mathrm{By}$  analysis of timed or hybrid automata, we mean reachability analysis unless otherwise stated.

of magnitude smaller than any time constraint required by the environment, they can be safely ignored.

However, clearly there are cases where making the synchrony hypothesis is just too unrealistic. In those circumstances, we have to make sure that the software will run appropriately, even on hardware with limited speed and relatively unreliable clocks.

One way of achieving this verification is to study the target hardware platform, and incorporate its limitations *into the controller model*. This can be quite difficult and time consuming, and the result might only be valid for one platform.

Another approach has been studied by Raskin et al. in [DDR05b], which works by using the synchrony hypothesis for the design of the controller, and by formally validating that hypothesis during the verification phase. This is achieved by using a special semantics for the controller automaton, called the  $Almost\ ASAP\ semantics$ . This approach is studied in detail in chapter 3.

# 1.6 Syntax and Semantics

The theoretical aspects of this work will rely heavily on the dual notions of syntax and semantics. In this work, what we call *syntax* is a formal definition of a *set of legal objects*. The syntax definition indicates which are legal objects and which are not. For example, the syntax of regular expressions is such that  $(a + b(cd)^*)$  and  $((ab)^+c)$  are considered legal, while  $((ab)^a)$  and  $((acd)^+)$  are not.

A syntax definition alone is meaningless without an associated semantics. The semantics definition creates a formal object, the form of which depends on the syntax. To continue with regular expression, the semantics of  $(a + b(cd)^*)$ , which we note  $[(a + b(cd)^*)]$  is the set of strings:  $\{a, b, bcd, bcdcd, bcdcdcd, ...\}$ .

The advantage of distinguishing syntax and semantics is clear: it is much more convenient to write  $(ab)^*(cd)^* + e^+f$ , than  $\{\epsilon, ab, abab, ababab, \dots, cd, cdcd, cdcdd, \dots, abcd, ababad, abababd, \dots, abcdcd, abcdcddd, \dots, ef, eef, eeef, \dots\}$ .

Moreover, the latter description is not only heavy and difficult to understand, it is also *ambiguous*<sup>2</sup>. This is why we use syntax definitions; to represent complex (and possibly infinite) mathematical objects (which are ultimately described by the semantics) in a concise and unambiguous manner.

In this work, we will not use regular expression to reason on software controllers, but rather *timed automata* and *timed transition systems*. Timed automata will provide syntax to our models, and we will define their semantics in the form of timed transition systems. As with timed automata, timed transition systems will be discussed in the next chapter.

<sup>&</sup>lt;sup>2</sup>This example is a bit overdone to stress the point. It is of course possible the express the language of the regular expression above in a totally unambiguous fashion.

# 1.7 AASAP Semantics and Implementability

As stated previously, the Almost ASAP semantics provides a means to formally validate the synchrony hypothesis. This approach works as follows:

- 1. A model for the controller is designed, using timed automata. At this point, we do not worry about the limitations of the hardware yet. This allows the designer to focus on control logic rather than implementation details, yielding simpler and more elegant models.

- 2. When the controller automaton and environment automata have been created, they are analyzed in the classical way by composing both automata and applying model-checking techniques. This analysis is made using the standard semantics for timed automata, which does not forbid unimplementable behaviors. A sequence of actions is considered unimplementable in our context, if it cannot be executed by hardware, no matter how fast it is or how precise its digital clocks are. These behaviors include for example: taking several discrete transitions consecutively, without letting time elapse; or taking transitions only at fixed points in time (this is unimplementable because it requires infinite clock-precision). Thus, this preliminary analysis can yield "correctness proofs" for controllers which cannot be used in practice.

- 3. To make sure that the control strategy can be be executed by hardware, we analyze the system a second time, but with this time using the Almost ASAP semantics for the controller. Using this semantics, it is be possible verify (with the help of automated tools) the correctness and implementability of control strategies expressed with timed automata<sup>3</sup>.

The reader might wonder why the second step is necessary. In fact, it is not. However, as analyzing the classical semantics of timed automata is much faster than with the Almost ASAP semantics, that second step is very useful in practice (because if it fails, the next step will certainly fail as well).

# 1.8 Implementing Controllers Systematically

We have stated earlier that one of the advantages of the top-down verification approach is that it is possible to create implementations in a systematic way. With the Almost ASAP semantics approach, this is achieved using an *implementation* semantics.

<sup>&</sup>lt;sup>3</sup>Actually, the Almost ASAP semantics is not exactly applied on timed automata but rather on one of its subclass, called Elastic controllers. The difference is quite small however, and will be detailed in the following chapters.

Once the control-logic of the controller has been proven correct and implementable, we give a third semantics to the controller's timed automaton, which does not only describe what the controller does, but also contains details on how this is achieved in practice. The purpose of the three semantics we have mentioned can be summarized as follows:

- The classical semantics enables us to ensure that a control strategy is sound in the context of the synchrony hypothesis.

- The Almost ASAP semantics enables us to verify that a control strategy remains sound, even when executed on hardware with limited speed and precision.

- The implementation semantics describes *how* the control strategy is executed by hardware and enables us to construct implementations in a systematic way.

In [DDR05b], Raskin et al. have demonstrated how their methodology can be used to create implementations in a systematic manner, by using a proof-of-concept implementation semantics, which they called *program semantics*. They successfully applied this methodology in practice, by creating a code generating tool<sup>4</sup> for the Lego Mindstorms<sup>TM</sup> platform.

## 1.9 Goal and Structure of this Work

The goal of this work is to study how the Almost ASAP semantics approach can be applied to more realistic embedded real-time platforms. The implementation semantics described in [DDR05b] has been voluntarily kept simple, and thus makes almost no hypothesis about the target run-time environment. As we will see in the following, the Almost ASAP semantics approach can be improved if we assume that the generated code will run on a hard real-time operating system. Our work will be structured as follows:

- In chapter 2, we define timed automata and their classical semantics. We will see how these automata are suitable for the design and analysis of real-time software and how this is done in practice.

- In chapter 3, we define the Almost ASAP semantics and the various definitions needed for its use. We will keep a to-the-point approach, by reviewing only the essential aspects which will be needed in this work.

<sup>&</sup>lt;sup>4</sup>The tool is available at http://www.ulb.ac.be/di/ssd/madewulf/aasap/

- In chapter 4, we define the Program Semantics, as described in [DDR05b]. This definition will be followed by a discussion analyzing how it can be improved in the context of real-time operating systems. We will then define a new implementation semantics, called unsurprisingly *Real-Time Semantics*, which takes advantage of the capabilities of an RTOS. To validate this new semantics formally, we provide a complete simulation proof with the Almost ASAP Semantics.

- In chapter 5, we present a modern hard real-time operating system, namely RTAI<sup>5</sup>. We briefly describe its architecture and a small subset of its API (this information is needed in the following chapter).

- In chapter 6, we present Spectre, a tool for generating provably correct real-time code which has been created to demonstrate the practical applicability of our work. We describe how a Spectre-generated controller uses the RTAI run-time environment to behave consistently with the Real-Time Semantics. We also describe the tool's input language, along with details illustrating how it generates code and in what respect this code can be considered provably correct.

- In chapter 7, we illustrate the use of Spectre with a case-study.

- In chapter 8, we conclude this work by a discussion reviewing the progress made in this work, and pointing out some suggestions as to how it could be improved.

- Appendix A contains the grammar of the Spectre input language.

- Appendix B contains an example of a Spectre-generated controller.

<sup>&</sup>lt;sup>5</sup>RTAI is freely available for download at http://www.rtai.org

# Chapter 2

# Timed Automata

This chapter introduces the theoretical background needed for the following chapters. Definitions are given for timed automata, as well as a number of their useful properties. In the final part of the chapter, we show how these computation models can be used in practice with a couple examples.

# 2.1 Syntax of Timed Automata

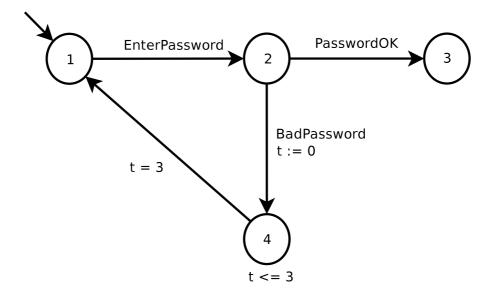

Timed automata are finite state automata extended with a finite number of *clocks*. When a timed automaton (TA) stays in one particular location, each of his clocks' value increases continuously with first derivative equal to one. As a discrete transition occurs, the TA can either reset a clock to zero, or leave it untouched. Before the formal definition, here is a small example of a timed automaton:

Figure 2.1: Simple example of a timed automaton.

This simple timed automaton has four locations and one clock: t. As indicated by the small arrow in the upper left part of the figure, location 1 is the initial location of this automaton. Three of the four transitions are labeled with a string; they materialize events that occur in the system. Labels and events will be treated in depth later in this chapter. Transition  $2 \to 4$  assigns the clock t to the value zero. Thus, while in location 4, the value of clock t increases continuously from zero onward. Exactly three time units later, t will hold the value 3 and the transition t will be enabled, because the predicate attached to it becomes true. When one of its transition becomes enabled a timed automaton can take that transition as long as it stays enabled. It is important to note that a TA does not have to take an enabled transition, and this often leads to non-deterministic behaviors. In this particular case, the automaton is fully deterministic thanks to the predicate attached to location 4. The automaton cannot refuse to fire transition t when t equals 3 without violating the predicate t is t.

#### Synchronization labels

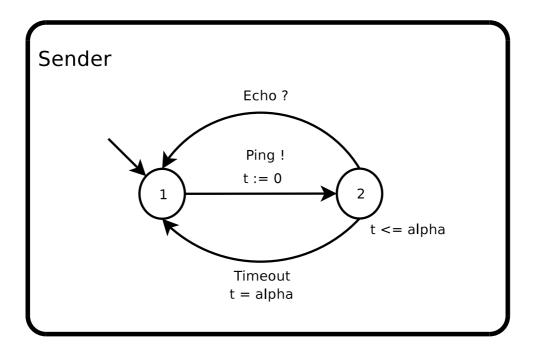

The edges of timed automata are sometimes tagged with strings. Their purpose can be purely informational (as in the example of figure 2.1), or they can be used to synchronize events with other automata. When modeling complex interacting systems, it is often convenient to model each system separately with its own TA. Then, a special operation called *synchronized product* (also called *parallel composition* in the literature) makes one big timed automaton with all the small ones. The synchronization labels provide a means of communication between the automata within the composition. This is best illustrated by an example.

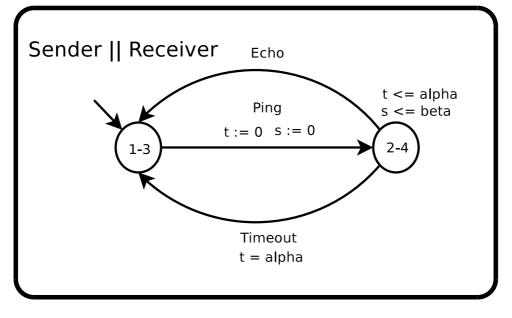

The example of figure 2.2 is a much simplified version of the ICMP<sup>1</sup> protocol. One station sends a "ping" packet to the other, which in turn responds with an "echo" reply. Observe that not all labels are used to synchronize the sender with the receiver: the label **Timeout** is not seen by the receiver. Throughout this work, we will use the popular convention of adding an exclamation mark after output messages, and a question mark after input messages. As illustrated by the figure, the synchronized product is a somewhat natural operation.

#### Guards and rate conditions

The control flow in timed automata is coerced by the predicates attached to its locations and edges. The edge predicates are often called *guards* in the literature. When a guard becomes true, the corresponding edge is said to be *enabled* and the automaton can follow that edge as long as it stays enabled. Location predicates are also often called *invariant predicates* in the literature. A timed automaton cannot be in a location unless its invariant predicate is true, and must thus leave its location whenever it becomes false. In the example of figure 2.2, the receiver

<sup>&</sup>lt;sup>1</sup>ICMP stands for Internet Control Message Protocol.

Figure 2.2: Illustration of synchronization labels and parallel composition.

automaton can delay the "echo" up to beta time units, as it can take transition  $4 \to 3$  without restriction (it is always enabled because its predicate is  $true^2$ ). It may not stay longer, however, without violating the invariant predicate of location 4.

#### Syntax definitions

Before defining the timed automaton, we need to precise what kind of predicates can be used in their definition. We will use a notion similar to the one introduced in [AD94], namely the rectangular clock predicate. Basically, with these predicates it is only possible to compare a clock to a positive rational value, or to a rational interval (possibly infinite). It is not permitted to compare two clocks directly for example. Here is the formal definition.

**Definition 1** [Rectangular Clock Constraint / Predicate] A rectangular clock constraint over a set of clocks X is a formula of the form  $x \in I$ , where I is a rational interval, open or closed and possibly infinite. Formally, I is of the form (a, b), [a, b), (a, b], or[a, b] with  $a, b \in \mathbb{Q}^{\geq 0} \cup \{+\infty\}$  and  $a \leq b$ .

A rectangular clock predicate is a finite set of rectangular clock constraints. For a rectangular clock predicate p and a clock valuation v, we write  $v \models p$  if  $v(x) \in I$  for every " $x \in I$ " appearing in p. Finally, the set of all rectangular clock predicates over a clock set X is noted Rect(X), and that same set but with closed intervals is noted  $\text{Rect}_{c}(X)$ .

Note that this definition is quite restrictive. It is not possible to express a disjunction directly with one predicate for instance. These restrictions are made to reduce the complexity of timed automata analysis. This phenomenon is well known: models that are too expressive quickly become undecidable. It is shown in [AD94], for instance that allowing to compare a rational value to the sum of two clocks leads to undecidability of timed automata analysis.

We are now ready to define the timed automaton formally.

**Definition 2** [Timed Automaton - Syntax] A timed automaton is a tuple  $\langle Loc, l_0, Var, Inv, Lab^{in}, Lab^{out}, Lab^{\tau}, Edg \rangle$  where :

- Loc is a finite set of locations.

- $l_0 \in Loc$  is the initial location.

- Var is a finite set of clocks, which are positive real-valued variables.

- Lab = Lab<sup>in</sup> $\cup$ Lab<sup>out</sup> $\cup$ Lab<sup> $\tau$ </sup> is a structured, finite alphabet of synchronization labels. It is partitioned into input output and internal labels, respectively.

<sup>&</sup>lt;sup>2</sup>Predicates that evaluate to *true* are omitted in the figures.

• Edg  $\subseteq$  Loc  $\times$  Loc  $\times$  Rect(Var)  $\times$  Lab  $\times$   $2^{\text{Var}}$  is a finite set of edges, also called transitions. The edge  $(l_1, l_2, g, \sigma, R)$  goes from location  $l_1$  to  $l_2$ , resets the clocks contained in R to zero and is enabled only when the clock guard g is true. Depending on the label  $\sigma$  attached to the edge, the transition represents the acceptance of an input  $(\sigma \in \mathsf{Lab}^\mathsf{in})$ , the emission of output  $(\sigma \in \mathsf{Lab}^\mathsf{out})$ , or an internal event  $(\sigma \in \mathsf{Lab}^\mathsf{r})$ .

# 2.2 Classical Semantics of Timed Automata

As mentioned in the introduction, the above syntax definition does not mean much without an associated semantics. As we will define several semantics for timed automata in this work (four in total), we will give a name to each to avoid ambiguity. We start by defining the *classical* semantics of timed automata.

#### Timed transition systems

To formalize the semantics of timed automata we will use timed transition systems (TTS). The TTS associated to a timed automaton captures two things: (1) the complete state space of the TA, and (2) for each state of that space, the TTS tells which states are reachable in one move<sup>3</sup>. The state space of a timed automaton is the set of all configurations it can have, i.e. its current location and the value of its clocks. As the clocks take their values from a dense set, the state space is almost always infinite<sup>4</sup>.

**Definition 3** [Timed Transition System] A timed transition system  $\mathcal{T}$  is a tuple  $\langle S, \iota, \Sigma, \rightarrow \rangle$  where :

- S is a (possibly infinite) set of states.

- $\iota \in S$  is the initial state.

- $\Sigma$  is a finite set of labels.

- $\rightarrow \subseteq S \times \Sigma \cup \mathbb{R}^{\geq 0} \times S$  is the transition relation with  $\mathbb{R}^{\geq 0}$  being the set  $\{x \in \mathbb{R} \mid x \geq 0\}$  of all non-negative real numbers.

$<sup>^{3}</sup>$ In this context, a *move* is understood as either a discrete jump or an arbitrarily small time increment

<sup>&</sup>lt;sup>4</sup>One could make a timed automaton which never lets time elapse, by taking an infinite number of transitions at time zero. Then indeed, the state space of that automaton would be finite.

Timed transition systems are very useful because they contain in a somewhat concise manner all the *possible behaviors* of a timed system. This notion of possible behavior is formalized by a *path*, and is defined as follows:

**Definition 4** [Path in TTS] A *finite path* in the timed transition system  $\mathcal{T} = \langle S, \iota, \Sigma, \rightarrow \rangle$  is a finite sequence alternating between state and transition labels, and is noted  $\lambda$ . Let  $\lambda = (s_0, \tau_0, s_1, \tau_1, \ldots, \tau_{n-1}, s_n)$ .  $\lambda$  is a finite path of  $\mathcal{T}$  if (1) for every  $i \in [0, n], s_i \in S$  and (2) for every  $i \in [0, n), (s_i, \tau_i, s_{i+1}) \in \rightarrow$ . The *length* of  $\lambda$  is n+1 and is denoted  $|\lambda|$ . This definition is extended to infinite paths in the obvious way and the length of such a path is  $+\infty$ . A path  $\lambda$  is *initial* if its first state is the initial state. We write  $\mathsf{Path}_{\mathsf{F}}(\mathcal{T})$  the set of all *finite initial paths* of  $\mathcal{T}$  and  $\mathsf{Path}_{\infty}(\mathcal{T})$  the set of all *infinite initial paths* of  $\mathcal{T}$ . The set of states which appear in  $\lambda$  is noted  $\mathsf{State}(\lambda)$

Now we can define the useful notion of reachability in TTS:

**Definition 5** [state-reachability in TTS] Let  $\mathcal{T} = \langle S, \iota, \Sigma, \rightarrow \rangle$  be a timed transition system and a state  $s \in S$ . The state s is reachable in  $\mathcal{T}$  if there exists a finite initial path  $\lambda = (s_0, \tau_0, s_1, \tau_1, \dots, \tau_{n-1}, s_n)$  such that  $s_n = s$ . The set of all reachable states in  $\mathcal{T}$  is noted Reach $(\mathcal{T})$ .

As stated in the introduction, the verification process we employ requires a composition of the interacting system models. We cannot perform this composition at the syntax level because the environment and controller semantics will not be the same. Hence, we need a way of composing timed transition systems. This composition requires a partitioning of the synchronization labels into three sets, so we refine our definition of TTS with a definition of structured timed transitions systems.

**Definition 6** [Structured Timed Transition System] A structured timed transition system (STTS)  $\mathcal{T}$  is a tuple  $\langle S, \iota, \Sigma^{\mathsf{in}}, \Sigma^{\mathsf{out}}, \Sigma^{\tau}, \rightarrow \rangle$  where :

- S is a (possibly infinite) set of states.

- $\iota \in S$  is the initial state.

- The set of labels is partitioned into input  $(\Sigma^{\text{in}})$  output  $(\Sigma^{\text{out}})$  and internal labels  $(\Sigma^{\tau})$ .

- $\to \subset S \times \Sigma^{\mathsf{in}} \cup \Sigma^{\mathsf{out}} \cup \Sigma^{\tau} \cup \mathbb{R}^{\geq 0} \times S$  is the transition relation.

Before formalizing the notion of composition mentioned earlier, we need to take a few precautions. We have seen that timed automata communicate through synchronization on common labels. This communication is blocking and we need to make sure that (1) no automaton deliberately refuses an input from another and (2) no automaton sends an output to one that cannot receive it. These issues are resolved by imposing *input enabledness* of the STTS.

**Definition 7** [Input Enabled STTS] A STTS  $\mathcal{T} = \langle S, \iota, \Sigma^{\mathsf{in}}, \Sigma^{\mathsf{out}}, \Sigma^{\tau}, \rightarrow \rangle$  is *input* enabled if it can accept any input symbol, at any time. Formally,  $\mathcal{T}$  must be such that for all  $\sigma \in \Sigma^{\mathsf{in}}$ , for all  $s_1 \in S$  there exists  $s_2 \in S$  such that  $(s_1, \sigma, s_2) \in \rightarrow$ .

We are now ready to define the composition of two STTS. Note that this definition can be extended to the composition of any number of STTS.

**Definition 8** [Composition of STTS] Consider two input enabled STTS  $\mathcal{T}_1 = \langle S_1, \iota_1, \Sigma_{2\to 1}, \Sigma_{1\to 2}, \Sigma_1^{\tau}, \to_1 \rangle$  and  $\mathcal{T}_2 = \langle S_2, \iota_2, \Sigma_{1\to 2}, \Sigma_{2\to 1}, \Sigma_2^{\tau}, \to_2 \rangle$ . The parallel composition of  $\mathcal{T}_1$  and  $\mathcal{T}_2$ , noted  $\mathcal{T}_1 || \mathcal{T}_2$  is the TTS  $\mathcal{T} = \langle S, \iota, \Sigma, \to \rangle$  such that :

- 1.  $S = \{(s_1, s_2) \mid s_1 \in S_1 \text{ and } s_2 \in S_2\} \text{ and } \iota = (\iota_1, \iota_2).$

- 2.  $\Sigma = \Sigma_{1\to 2} \cup \Sigma_{2\to 1} \cup \Sigma_1^{\tau} \cup \Sigma_2^{\tau}$ .

- 3. For every  $\sigma \in \Sigma \cup \mathbb{R}^{\geq 0}$ , we have that  $((s_1, s_2), \sigma, (s'_1, s'_2) \in \rightarrow \text{ iff one of the following assertions holds}:$

- [Internal move of  $\mathcal{T}_1$ ]  $\sigma \in \Sigma_1^{\tau}$  and  $(s_1, \sigma, s_1') \in \to_1$  and  $s_2' = s_2$ .

- [Internal move of  $\mathcal{T}_2$ ]  $\sigma \in \Sigma_2^{\tau}$  and  $(s_2, \sigma, s_2') \in \to_2$  and  $s_1' = s_1$ .

- [Synchronized move]  $\sigma \in \Sigma_{1\to 2} \cup \Sigma_{2\to 1} \cup \mathbb{R}^{\geq 0}$  and  $(s_1, \sigma, s_1') \in \to_1$  and  $(s_2, \sigma, s_2') \in \to_2$ .

Definition 8 is rather straightforward. In the composition, a STTS can fire internal events without disturbing the other and vice versa. The third assertion in the definition of  $\rightarrow$  ensures that (1) synchronization on common labels does happen correctly, and (2) that time elapses identically on both sides.

#### Classical semantics of timed automata

We are now ready to give a semantics definition to timed automata. Bear in mind that several other semantics will be used in the following chapters, here we define what is called the *classical* semantics of timed automata.

**Definition 9** [Timed Automata - Classical Semantics] The classical semantics of the timed automaton  $A = \langle \mathsf{Loc}, l_0, \mathsf{Var}, \mathsf{Inv}, \mathsf{Lab^{in}}, \mathsf{Lab^{out}}, \mathsf{Lab^{\tau}}, \mathsf{Edg} \rangle$ , noted  $[\![A]\!]$ , is the STTS  $\langle S, \iota, \Sigma^{\mathsf{in}}, \Sigma^{\mathsf{out}}, \Sigma^{\tau}, \rightarrow \rangle$  where :

- $S = \{(l, v) \mid l \in \mathsf{Loc} \text{ and } v \text{ is a valuation of the clocks in } \mathsf{Var} \text{ such that } v \models \mathsf{Inv}(l)\}.$

- $\iota = (l_0, v_0)$  with  $v_0$  being a valuation of the clocks in Var assigning the value zero to each clock.

- $\Sigma^{\text{in}} = \mathsf{Lab}^{\text{in}}, \Sigma^{\text{out}} = \mathsf{Lab}^{\text{out}}, \Sigma^{\tau} = \mathsf{Lab}^{\tau}$ .

- For every  $\sigma \in \Sigma^{\text{in}} \cup \Sigma^{\text{out}} \cup \Sigma^{\tau} \cup \mathbb{R}^{\geq 0}$ , the transition  $((l, v), \sigma, (l', v')) \in \to$  iff one of the following assertions holds:

- $-\sigma \in \Sigma^{\text{in}} \cup \Sigma^{\tau} \cup \Sigma^{\text{out}}$  and there exists an edge  $(l, l', g, \sigma, R) \in \mathsf{Edg}$  with  $v \models g$  and v' being the same valuation than v but assigning the value zero to the clocks in R.

- The edge mentioned above doesn't exist,  $\sigma \in \Sigma^{in}$  and (l', v') = (l, v).

- $-\sigma \in \mathbb{R}^{\geq 0}$ , l' = l and for each clock  $x \in \text{Var}$  we have that (1) v'(x) = v(x) + t and (2)  $\forall t' \in [0, t] : v + t' \models \text{Inv}(l)$ .

Notice how definition 9 formalizes the intuitions given previously. The semantic state space of the timed automaton (S in the definition) is the set of all configurations (i.e. location and clock valuation) which satisfy the invariant predicates. Transitions can occur along enabled edges, which is only the case when their guard is satisfied by the current clock valuation. The syntactic component R of an edge indicates which clocks need to be reset after taking that edge. A timed automaton can stay in (or enter) a location if and only if the corresponding location predicate is satisfied. Finally, observe that our definition of the classical semantics of timed automata is input-enabled: if an input arrives and no edge specifies what to do, an implicit self-loop occurs (as stated by the second assertion in the definition of  $\rightarrow$ ).

#### Illustration of the semantics definition

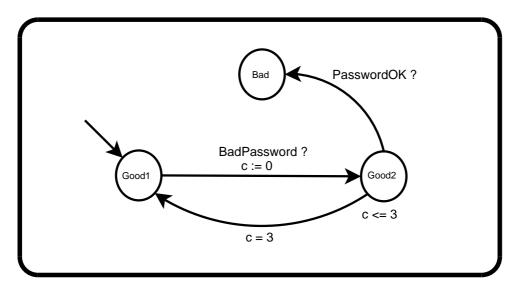

This definition is essential to the following chapters so we illustrate with an example. Let A be the timed automaton depicted in figure 2.1. The syntax of that automaton has not been given formally but it is straightforward. Its classical semantics is the STTS  $[\![A]\!] = \langle S, \iota, \Sigma^{\mathsf{in}}, \Sigma^{\mathsf{out}}, \Sigma^{\tau}, \to \rangle$  where :

- $S = \{(l, v) \mid l \in \{1, 2, 3\}, v(t) \in [0, +\infty)\} \cup \{(4, v) \mid v(t) \in [0, 3]\}$

- $\iota = (1, v_0)$  with  $v_0(t) = 0$

- $\Sigma^{\mathsf{in}} = \Sigma^{\mathsf{out}} = \phi$ ,  $\Sigma^{\tau} = \{\epsilon, \mathsf{EnterPassword}, \mathsf{BadPassword}, \mathsf{PasswordOK}\}$

```

\begin{array}{ll} \bullet & \to = & \{((1,v), \mathsf{EnterPassword}, (2,v)) \mid v(t) \in [0,+\infty)\} \\ & \cup & \{((2,v), \mathsf{PasswordOK}, (2,v)) \mid v(t) \in [0,+\infty)\} \\ & \cup & \{((2,v), \mathsf{BadPassword}, (4,v')) \mid v(t) \in [0,+\infty), v'(t) = 0\} \\ & \cup & \{((4,v),\epsilon,(1,v)) \mid v(t) = 3\} \\ & \cup & \{((l,v),\delta,(l,v+\delta)) \mid \delta \in \mathbb{R}^{\geq 0}, l \in \{1,2,3\}, v(t) \in [0,+\infty)\} \\ & \cup & \{((4,v),\delta,(l,v+\delta)) \mid \delta \in \mathbb{R}^{\geq 0}, v + \delta(t) \in [0,3]\} \\ \end{array}

```

# 2.3 Timed Systems Analysis

When using timed automata to analyze a timed system, we are generally interested not only by the model itself but by the formal properties that can be inferred from it. For example, an interesting property of the automaton of figure 2.1 could be phrased as "A brute-force attack of n password attempts requires at least 3n time units". Of course, we usually want to be more formal and this section will show how properties are defined and used in practice.

Formal specifications have many kind of properties and this work will mainly focus on one kind: safety properties. A safety property requires a formal system to stay in a predefined subset of the state space, which is usually referred as the safe states or good states. These kind of properties are very useful in practice and suffice for many applications. One notable exception where safety properties are not enough is the liveness (or fairness) type of property, which requires the model to actually do what it is supposed to, in a finite amount of time, and to have no deadlock<sup>5</sup>.

To define safety properties formally, we need to extend the notion of reachability of definition 5 to regions. A region of a timed transition system is a subset of its state space. A region R is reachable in the TTS  $\mathcal{T}$  if  $R \cap \mathsf{Reach}(\mathcal{T}) \neq \phi$ .

**Definition 10** [Safety Property in TTS] Let  $\mathcal{T} = \langle S, \iota, \sigma, \rightarrow \rangle$  and let  $R \subseteq S$  be a region representing a set of good states.  $\mathcal{T}$  is safe for R iff  $\mathsf{Reach}(\mathcal{T}) \subseteq R$ .

In practice, we use algorithms which compute  $\mathsf{Reach}(\mathcal{T})$ , and determine if that set has an intersection with the complement of R in S. The set  $\bar{R} = S \setminus R$  is often called the set of bad states.

To formalize properties in a natural way, we usually use what is called a *monitor* automaton. This automaton usually consists of two states: Good and Bad with one edge going from the first to the second. On that edge we attach a predicate corresponding to the negation of the property we want to verify. That monitor automaton is then included in the composition, along with the other agents in the system and we compute a reachability analysis to verify if indeed

<sup>&</sup>lt;sup>5</sup>Indeed, a model which sits forever in its initial state (provided that state is safe) trivially satisfies any safety property. This is usually easily detected, however, and does not always need to be verified formally.

Bad is never reachable. Of course, some safety properties will be complex enough so that they cannot be expressed with only one clock predicate, and in that case a bigger monitor automaton will be needed.

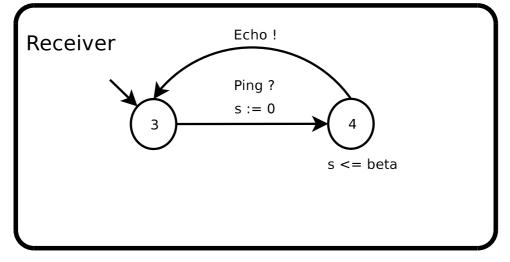

For example, to formalize the property mentioned previously, the monitor automaton of figure 2.3 would work. To express the property accurately, it needs three states.

Figure 2.3: Example monitor automaton.

## 2.4 Timed Automata in the Literature

This chapter only scratched the surface of the theory of timed automata. To keep this work at a reasonable size, we have only given the few definitions needed for the understanding of the following chapters. We have not described, for instance, how timed automata can be analyzed effectively using automated tools. This information, along with decidability results, can be found for example in [BY04] and [AD94].

# Chapter 3

# Implementability of Timed Controllers

The final goal of this work is to develop a methodology for building real-time embedded software with formal assurance that it will work as intended. In the previous chapter, we have seen that timed automata can be used to provide a model for the controller and its environment and that it is possible to obtain formal assurance that this model is *correct*, in the sense that it satisfies some formal requirement.

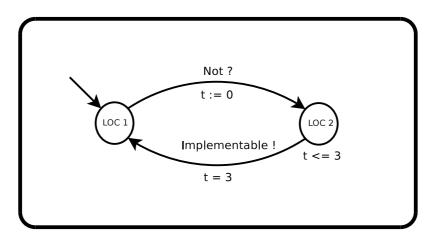

However, as stated in the introduction, this proof of correctness is only valid in the context of the synchrony hypothesis. This is because the classical semantics of timed automata allows unimplementable behaviors. Consider the following controller:

Figure 3.1: This timed automaton has a classical semantics that is not implementable because it requires an infinite clock precision, which any hardware is incapable of.

This controller is obviously not implementable and it illustrates one reason

for this: any computer hardware has clocks with *finite precision*. The clocks of timed automata take their values from a dense set, whereas hardware clocks are always discrete and thus have limited precision. If the correctness of a control strategy relies on infinite time precision, then it will not be implementable. We need to make sure that clock-rounding errors will not induce bad behaviors of the controller.

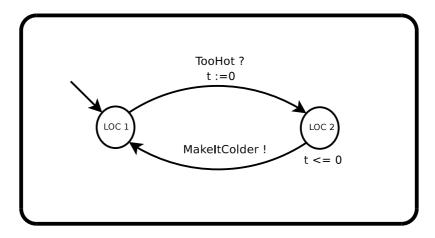

Infinite clock precision is not the only cause of unimplementability, as illustrated by this controller :

Figure 3.2: This second example illustrates the unimplementability caused by the instantaneity required by the classical semantics. The classical semantics of timed automata requires that these two transitions be taken in zero time units which is impossible on any hardware.

This last example does not require infinite clock-precision (even digital clocks can hold an exact null value) and yet it is not implementable. This is because until now we have considered that the communication between the interacting components of the system was *instantaneous*. This is very convenient at the modeling level, but again it needs to be formally validated. Communications in real implementations will always introduce delays and we need to make sure that the control strategy remains correct when they happen.

The synchrony hypothesis can be seen as an undesirable "side-effect" of the classical semantics of timed automata. This problem could be solved by taking the hardware limitation into account in the controller design process. This amounts to make *syntactic* changes to the controller automaton, by adding enough nodes, clocks, predicates and edges in order to obtain a implementable model.

The Almost ASAP semantics approach suggests a different path; it incorporates the hardware limitations the target platform by the means of a *semantics* change. This is very convenient because it keeps the controller automaton free of implementation details.

# 3.1 Overview of the Almost ASAP Approach

Recall the classical semantics of timed automata defined in the previous chapter. This semantics interprets the syntax in the most obvious manner; an edge guarded by the predicate t=3 can only be taken when t is exactly 3. Similarly, the classical semantics makes the emission of an output event correspond to its arrival to the receiver at the exact same time. The idea behind the Almost ASAP semantics is to make an interpretation of the syntax that is more relaxed; by allowing some bounded imprecision on the guard evaluation mechanism, and some bounded delay during synchronization on common labels, the almost ASAP semantics makes the control strategy something which can be executed by hardware.

The Almost ASAP semantics is parametric, it takes a real-valued parameter noted  $\Delta$ , which represents a superior bound on both the time-imprecision of the hardware and communication delay. This parameter is used throughout the semantics, extending its possible behaviors to a wider range. For example, with the AASAP semantics the interpretation of every guard of the automaton is enlarged by the parameter  $\Delta$ . An edge with a guard predicate t=3 will be traversable when  $t \in [3-\Delta, 3+\Delta]$ . So, if the time imprecision of the hardware is bounded by  $\Delta$ , the controller implementation will have a chance to take the edge appropriately. The AASAP semantics also makes a distinction between the emission of an event and its arrival. This is done by duplicating event labels: one set corresponds to the emissions, and the other to the actual treatments by the receivers. When an event is emitted by the environment, the almost ASAP semantics allows the controller to wait up to  $\Delta$  time units before taking that event into account. This represents the time needed for the hardware to detect the event appropriately.

Suppose we have a controller modeled with a timed automaton A. We can prove that  $\llbracket A \rrbracket$  satisfies some properties, but we cannot do so directly for its almost ASAP semantics :  $\llbracket A \rrbracket_{\Delta}^{\mathsf{AAsap}}$ . To be able to analyze the almost ASAP semantics effectively with the tools and theories available, we need a way of transforming A into some A' such that  $\llbracket A' \rrbracket$  is somehow similar to  $\llbracket A \rrbracket_{\Delta}^{\mathsf{AAsap}}$ . In this work, we will use simulations - and the dual notion of refinement - to formalize this similarity.

## 3.2 Simulation and Controller Refinement

In the previous chapter, we have defined the structured timed transition system, which in our context is used to represent the timed state space of the controllers and environments we want to model. The STTS describes for each state, which states are reachable in one transition - discrete or continuous. The possible behaviors of an STTS is represented by the set of all its initial paths. The concept of simulation is closely related to initial paths; intuitively, an STTS A

can simulate another STTS B if every initial path of B is also an initial path of A. In short, in order for A to simulate B it must have at least as much possible behaviors as B. The notion simulation is defined formally by constructing a relation between the state spaces of the two STTS:

**Definition 11** [Simulation relation for STTS] Given two STTS,  $\mathcal{T}_1 = \langle S_1, \iota_1, \Sigma_1^{\mathsf{in}}, \Sigma_1^{\mathsf{out}}, \Sigma_1^{\tau}, \to_1 \rangle$  and  $\mathcal{T}_2 = \langle S_2, \iota_2, \Sigma_2^{\mathsf{in}}, \Sigma_2^{\mathsf{out}}, \Sigma_2^{\tau}, \to_2 \rangle$ , let  $\Sigma = \Sigma_1^{\mathsf{out}} \cup \Sigma_1^{\mathsf{in}} \cup \Sigma_1^{\tau}$ , we say that  $\mathcal{T}_2$  is *simulable* by  $\mathcal{T}_1$ , noted  $\mathcal{T}_2 \sqsubseteq \mathcal{T}_1$ , if there exists a relation  $R \subseteq S_2 \times S_1$  (called a *simulation relation*) such that:

- $(\iota_2, \iota_1) \in R$ ;

- for any  $(s_2, s_1) \in R$ , for any  $\sigma \in \Sigma \cup \mathbb{R}^{\geq 0}$ , for any  $s'_2$  such that  $(s_2, \sigma, s'_2) \in \to_2$ , there exists  $s'_1 \in S_1$  such that  $(s_1, \sigma, s'_1) \in \to_1$  and  $(s'_2, s'_1) \in R$ .

When two STTS can simulate each other, we say that they are *mutually* similar, but this will not be needed in the following. The similarity we have defined is sufficient in our context because it preserves safety properties.

To reason on preservation of safety properties, it is convenient to think in terms of *refinement*. The notion of refinement is dual to that of simulation; if  $B \sqsubseteq A$ , i.e. A can simulate B, then we say that B refines A, in the sense that B has less possible behaviors than A. Safety properties which are satisfied by an STTS are also satisfied by any refined version of that STTS. In fact, simulation relations even preserve stronger properties such as the ones that can be expressed with LTL formulas.

Recall from definition 10 that an STTS  $\mathcal{T}$  is safe for a region R iff  $\mathsf{Reach}(\mathcal{T}) \subseteq R$ . The preservation of safety properties is formalized as follows:

**Theorem 1** Let  $\mathcal{T}_1 = \langle S_1, \iota_1, \Sigma_1^{\text{in}}, \Sigma_1^{\text{out}}, \Sigma_1^{\tau}, \rightarrow_1 \rangle$ ,  $\mathcal{T}_2 = \langle S_2, \iota_2, \Sigma_2^{\text{in}}, \Sigma_2^{\text{out}}, \Sigma_2^{\tau}, \rightarrow_2 \rangle$  be two STTS such that  $\mathcal{T}_1 \sqsubseteq \mathcal{T}_2$ . If  $\mathcal{T}_2$  is safe for a region  $R \subseteq S_2 \subseteq S_1$  then  $\mathcal{T}_1$  is also safe for R.

This theorem will be extremely useful in the following. Recall that our ultimate goal is to generate provably correct code in a systematic fashion. As we have seen in the introduction, this will require the use of an implementation semantics, which details how the hardware executes the control strategy described by the corresponding timed automaton. To verify the soundness of the implementation semantics, we will use simulation proofs. Indeed, if we can prove that an implementation semantics is simulable by the AASAP, then we will not need to verify the safety of that implementation semantics, thanks to the above theorem. Such a simulation proof will be given for the Real-Time Semantics in the next chapter.

## 3.3 Elastic Controllers and ASAP Semantics

As seen in the previous chapter, invariant predicates can be attached to the nodes of a timed automaton to force it to leave its location. This was necessary in order to obtain a controller which does not idle constantly. A simpler way to work with timed automata is to remove invariants completely and assume an ASAP behavior. This ASAP semantics makes the automaton take every action as soon as possible, thus removing the need for invariant predicates completely. In [DDR05b], controllers are modeled with this subclass of timed automata, and are called Elastic controllers.

**Definition 12** [ELASTIC Controller] An Elastic controller A is a tuple  $\langle \mathsf{Loc}, l_0, \mathsf{Var}, \mathsf{Lab^{in}}, \mathsf{Lab^{out}}, \mathsf{Lab^{\tau}}, \mathsf{Edg} \rangle$  where:

- Loc is a finite set of locations;

- $l_0 \in Loc$  is the initial location;

- $Var = \{x_1, \dots, x_n\}$  is a finite set of clocks;

- Lab = Lab<sup>in</sup>  $\cup$  Lab<sup>out</sup>  $\cup$  Lab<sup> $\tau$ </sup> is a finite structured alphabet of labels, partitioned into input labels Lab<sup>in</sup>, output labels Lab<sup>out</sup>, and internal labels Lab<sup> $\tau$ </sup>;

- Edg is a set of edges of the form  $(l, l', g, \sigma, R)$  where  $l, l' \in \mathsf{Loc}$  are locations,  $\sigma \in \mathsf{Lab}$  is a label,  $g \in \mathsf{Rect}_{\mathsf{c}}(\mathsf{Var})$  is a guard and  $R \subseteq \mathsf{Var}$  is a set of clocks to be reset.

Note that Elastic controllers only use *closed* rectangular predicates. This is because in our context of finite clock-precision, comparing a clock to a non-closed rational interval does not make sense.

### 3.4 Almost ASAP Semantics

Before defining the AASAP semantics we need a couple more definitions:

**Definition 13** [True Since] We define the function "True Since", noted TS:  $[Var \to \mathbb{R}^{\geq 0}] \times Rect_c(Var) \to \mathbb{R}^{\geq 0} \cup \{-\infty\}$ , as follows:

$$\mathsf{TS}(v,g) = \left\{ \begin{array}{ll} t & \text{if } v \models g \land v - t \models g \land \forall t' > t : v - t' \not\models g \\ -\infty & \text{otherwise} \end{array} \right.$$

This TS function will be used in the AASAP semantics definition to express that the controller must take action when the predicate of an outgoing edge has been true long enough. Recall that the AASAP semantics allows a delay of up to  $\Delta$  time units before taking a transition.

To represent the clock imprecision, the guards attached to the edges of the elastic controller are enlarged. This is formalized as follows:

**Definition 14** [Guard Enlargement] Let g(x) be the rectangular constraint " $x \in [a,b]$ ", the rectangular constraint  $\Delta g(x)_{\Delta}$  with  $\Delta \in \mathbb{Q}^{\geq 0}$  is the formula " $x \in [a-\Delta,b+\Delta]$ " if  $a-\Delta \geq 0$  and " $x \in [0,b+\Delta]$ " otherwise. If g is a closed rectangular predicate then  $\Delta g_{\Delta}$  is the set of closed rectangular constraints  $\{\Delta g(x)_{\Delta} \mid g(x) \in g\}$ .

We are now ready to define the AASAP semantics. Intuitions are given right after the definition.

**Definition 15** [AASAP semantics] Given an Elastic controller

$$A = \langle \mathsf{Loc}, l_0, \mathsf{Var}, \mathsf{Lab^{in}}, \mathsf{Lab^{out}}, \mathsf{Lab^{\tau}}, \mathsf{Edg} \rangle$$

and  $\Delta \in \mathbb{Q}^{\geq 0}$ , the AASAP semantics of A, noted  $[\![A]\!]_{\Delta}^{\mathsf{AAsap}}$  is the STTS

$$\mathcal{T} = \langle S, \iota, \Sigma^{\mathsf{in}}, \Sigma^{\mathsf{out}}, \Sigma^{\tau}, \to \rangle$$

where:

- (A1) S is the set of tuples (l, v, I, d) where  $l \in \mathsf{Loc}, v \in [\mathsf{Var} \to \mathbb{R}^{\geq 0}], I \in [\Sigma^{\mathsf{in}} \to \mathbb{R}^{\geq 0} \cup \{\bot\}]$  and  $d \in \mathbb{R}^{\geq 0}$ ;

- (A2)  $\iota = (l_0, v, I, 0)$  where v is such that for any  $x \in \mathsf{Var} : v(x) = 0$ , and I is such that for any  $\sigma \in \Sigma^{\mathsf{in}}$ ,  $I(\sigma) = \bot$ ;

- (A3)  $\Sigma^{\mathsf{in}} = \mathsf{Lab^{\mathsf{in}}}, \ \Sigma^{\mathsf{out}} = \mathsf{Lab^{\mathsf{out}}}, \ \mathrm{and} \ \Sigma^{\tau} = \mathsf{Lab^{\tau}} \cup \overline{\mathsf{Lab^{\mathsf{in}}}} \cup \{\epsilon\};$

- (A4) The transition relation is defined as follows:

- for the discrete transitions, we distinguish five cases:

- (A4.1) let  $\sigma \in \mathsf{Lab}^\mathsf{out}$ . We have  $((l, v, I, d), \sigma, (l', v', I, 0)) \in \to \mathsf{iff}$  there exists  $(l, l', g, \sigma, R) \in \mathsf{Edg}$  such that  $v \models_{\Delta} g_{\Delta}$  and v' = v[R := 0];

- (A4.2) let  $\sigma \in \mathsf{Lab^{in}}$ . We have  $((l, v, I, d), \sigma, (l, v, I', d)) \in \to \mathsf{iff}$   $\cdot \mathsf{either}\ I(\sigma) = \bot \mathsf{and}\ I' = I[\sigma := 0];$

- · or  $I(\sigma) \neq \bot$  and I' = I.

- (A4.3) let  $\bar{\sigma} \in \overline{\mathsf{Lab^{in}}}$ . We have  $((l, v, I, d), \bar{\sigma}, (l', v', I', 0)) \in \to \text{ iff there}$  exists  $(l, l', g, \sigma, R) \in \mathsf{Edg}$ ,  $v \models_{\Delta} g_{\Delta}$ ,  $I(\sigma) \neq \bot$ , v' = v[R := 0] and  $I' = I[\sigma := \bot]$ ;

- (A4.4) let  $\sigma \in \mathsf{Lab}^{\tau}$ . We have  $((l, v, I, d), \sigma, (l', v', I, 0)) \in \to \text{ iff there}$  exists  $(l, l', g, \sigma, R) \in \mathsf{Edg}, v \models_{\Delta} g_{\Delta}, \text{ and } v' = v[R := 0]$ ;

- (A4.5) let  $\sigma = \epsilon$ . We have for any  $(l, v, I, d) \in S : ((l, v, I, d), \epsilon, (l, v, I, d)) \in \rightarrow$ .

- for the continuous transitions:

- (A4.6) for any  $t \in \mathbb{R}^{\geq 0}$ , we have  $((l, v, I, d), t, (l, v + t, I + t, d + t)) \in \rightarrow$  iff the two following conditions are satisfied:

- · for any edge  $(l, l', g, \sigma, R) \in \mathsf{Edg}$  with  $\sigma \in \mathsf{Lab}^{\mathsf{out}} \cup \mathsf{Lab}^{\tau}$ , we have that:

$$\forall t': 0 \leq t' \leq t: (d+t' \leq \Delta \vee \mathsf{TS}(v+t',g) \leq \Delta)$$

• for any edge  $(l, l', g, \sigma, R) \in \mathsf{Edg}$  with  $\sigma \in \mathsf{Lab^{in}}$ , we have that:  $\forall t' : 0 \le t' \le t : (d+t' \le \Delta \lor \mathsf{TS}(v+t', g) \le \Delta \lor (I+t')(\sigma) \le \Delta)$

## Comments on the AASAP semantics definition

- (A1) The state space is made of 4-tuples (l, v, I, d). l and v are the location and clock-valuation as in the classical semantics. I is vector assigning a real value to every input label, representing the time elapsed since the last untreated occurrence of that label, or  $\bot$  if there is no pending occurrence of that label. The AASAP semantics does not react instantaneously to input events, so it needs to remember how long it has delayed an input. The value d holds the time elapsed since the last location change occurred. That value will be used to delay edge crossings; the controller can ignore an enabled edge if d is smaller than  $\Delta$ .

- (A2) The initial location definition is straightforward.

- (A3) As mentioned previously, the AASAP semantics duplicates input labels. A distinction is made between the emission of an output label  $\sigma$  and its reception as an input label  $\overline{\sigma}$  by the controller. When the input is actually received, it is treated as an internal event, hence Lab<sup>in</sup> is added to  $\Sigma^{\tau}$ .

- (A4.1) To cross an edge tagged with an output label, the current clock valuation must satisfy the corresponding guard predicate, enlarged by  $\Delta$ . The notation v' = v[R := 0] means that v' is the same valuation than v but assigning the value 0 to the clocks in R. This behavior is exactly the same as in the usual semantics, except for the guard enlargement.

- (A4.2) This rule indicates what happens when a label is emitted by the environment. In the normal case, the corresponding value in I is set to zero. If

more than one input of the same kind is received before the controller had the chance to treat the first one, the semantics simply ignores the others and the "older" value in I is kept. Note that no edge is crossed at this point, the controller stays in its location for now. Also, this rule alone ensures the input enabledness of the controller.

- (A4.3, 4, 5) These rules should be clear with the previous comments.

- (A4.6) The previous rules defined when the controller can take action, this rule states when it must do so. It can let t time units elapse and not take a transition only if (1) the controller made a location change less than  $\Delta$  time units ago:  $d+t \leq \Delta$ ; or (2) there are no enabled outgoing edge, or if there are enabled outgoing edges, they have been enabled for less than  $\Delta$  time units:  $\mathsf{TS}(v+t,g) \leq \Delta$ . Also, the controller cannot delay the treatment of an input event more than  $\Delta$  time units:  $(I+t')(\sigma) \leq \Delta$ .

# Summary of the Almost ASAP semantics

Let us summarize the previous formal definition. In our methodology, control strategies are expressed using a syntax that is free of invariant predicates. The controller always tries to take a transition as soon as it can thus, almost as soon as possible. The "almost" is quantified by the parameter  $\Delta$ , which is the upper bound on three different delays or time imprecisions:

- The controller can wait up to Δ time units between two location changes, no matter the outgoing edge guards. This represents the fact that CPUs are not infinitely fast; a "location change" in the real world takes up a few processor cycles. It would be unreasonable to qualify a semantics allowing an infinite number of location changes in a finite amount of time as implementable.

- Since digital clocks aboard real computers have finite precision, every edge of the controller is enlarged by the value  $\Delta$ . If clock-rounding errors are guaranteed to be always smaller than  $\Delta$ , then then controller implementation will be able to cross the edge appropriately in all situations, despite the imprecision of its clocks.

- Finally, the almost ASAP semantics models communication delays that can be as large as  $\Delta$ . Each time an input arrives, the controller can wait up to  $\Delta$  time units before taking the corresponding edge, thus taking the input into account.

## Example

As with the Classical Semantics, we illustrate the Almost AASAP Semantics definition with an example. Again, we use the timed automaton of figure 2.1 but with a minor modification : consider EnterPassword as an input label and BadPassword and PasswordOK as output labels. Also, as we work with an ELASTIC controller this time, the predicate attached to location 4 is removed. To simplify the notations, consider that the clock valuation v and the input delay vector I are real values - I can still have the value  $\bot$ . There is only one clock and input label in this example so this works fine. Finally, in the definition of  $\to$ , assume that the free variables which are not quantified on the right hand side of the set definitions are simply non-negative real values. The Almost ASAP semantics of that ELASTIC controller is the structured timed transition system  $\llbracket A \rrbracket_{\Delta}^{\mathsf{AAsap}} = \langle S, \iota, \Sigma^{\mathsf{in}}, \Sigma^{\mathsf{out}}, \Sigma^{\tau}, \to \rangle$  where :

```

\bullet \ S = \{(l,v,I,d) \mid l \in \{1,2,3,4\}, v,d \in \mathbb{R}^{\geq 0}, I \in \{\mathbb{R}^{\geq 0} \cup \bot\}\}

```

```

• \iota = (1, 0, \bot, 0)

```

```

• \Sigma^{\mathsf{in}} = \{\mathsf{EnterPassword}\}, \Sigma^{\mathsf{out}} = \{\mathsf{EnterPassword}, \mathsf{BadPassword}\}, \Sigma^{\tau} = \{\epsilon\}

```

```

\{((l, v, \bot, d), \mathsf{EnterPassword}, (l, v, 0, d)) \mid l \in \{1, 2, 3, 4\}\}

(1)

\bigcup

\{((l, v, I, d), \text{EnterPassword}, (l, v, I, d)) \mid l \in \{1, 2, 3, 4\}\}

(2)

\{((1, v, I, d), \overline{\mathsf{EnterPassword}}, (2, v, \bot, 0))\}

(3)

\bigcup

\{((2, v, I, d), \mathsf{PasswordOK}, (3, v, I, 0)) \mid I \in \{\mathbb{R}^{\geq 0} \cup \bot\}\}

\bigcup

(4)

\{((2,v,I,d),\mathsf{BadPassword},(4,0,I,0))\mid I\in\{\mathbb{R}^{\geq 0}\cup\bot\}\}

\bigcup

(5)

\{((4, v, I, d), \epsilon, (1, v, I, 0)) \mid v \in [3 - \Delta, 3 + \Delta], I \in \mathbb{R}^{\geq 0} \cup \bot\}\}

U

(6)

\bigcup

\{((1, v, \bot, d), t, (1, v + t, \bot, d + t))\}

(7)

\{((1, v, I, d), t, (1, v + t, I + t, d + t)) \mid I \in \{\mathbb{R}^{\geq 0} \cup \bot\}, I + t \leq \Delta\}

\bigcup

(8)

\{((2, v, I, d), t, (2, v + t, I + t, d + t)) \mid I \in \{\mathbb{R}^{\geq 0} \cup \bot\}, d + t \leq \Delta\}

\bigcup

(9)

\{((3, v, I, d), t, (3, v + t, I + t, d + t)) \mid I \in \{\mathbb{R}^{\geq 0} \cup \bot\}\}

\bigcup

(10)

\{((4, v, I, d), t, (4, v + t, I + t, d + t)) \mid I \in \{\mathbb{R}^{\geq 0} \cup \bot\}, v + t \leq 3\}

\bigcup

(11)

\{((4, v, I, d), t, (4, v + t, I + t, d + t)) \mid I \in \{\mathbb{R}^{\geq 0} \cup \bot\}, d + t \leq \Delta\}

\bigcup

(12)

```

#### Comments on the discrete transitions

- (1) The controller waits for the input event EnterPassword. When it arrives, I is set to zero but no location change occurs yet. Notice that there is no restriction on the location here; the controller can receive the input EnterPassword at any time, ensuring input-enabledness.

- (2) As stated by the semantics, the controller ignores the subsequent emissions of an untreated input symbol; I and d are left untouched (We know that there is an untreated occurrence of the input symbol because I is a real value and not  $\bot$ ).

- (3) This set of transitions represent what happens when the controller has taken the input into account. I is reset back to  $\bot$ , d is reset to zero, and the location changes from 1 to 2.

- (4) There is no guard attached to the edge  $2 \to 3$ , so this transition can be taken for any valuation v. It is important to note however, that this does not mean that the controller can delay the emission indefinitely; at some point it will *have* to make that transition when the transition relation  $\to$  does not allow it to let time pass anymore.

- (5) This works just the same as the previous one, except that we reset the clock valuation as required by the edge  $2 \rightarrow 4$ .

- (6) The edge 4 → 1 illustrates how the guard enlargement works. This

edge is enabled as long as the clock valuation satisfies the enlarged guard

predicate.

#### Comments on the continuous transitions

- (7) Since the only outgoing edge of location 1 corresponds to an input, the controller can wait there indefinitely, as long as no input has arrived, i.e. as long as  $I = \bot$ .

- (8) When in location 1, the controller can delay an untreated input for as long as  $\Delta$  time units but not longer.

- (9) When in location 2, the controller faces two outgoing edges that are always enabled. The classical semantics would require it to fire one of the two immediately. Here, we allow the controller to stay in the location 2 for as long as d does not grow larger than  $\Delta$ .

- (10) As there is no outgoing edge in location 3, the Almost ASAP controller can of course let time pass indefinitely.

- (11) This one is a little more subtle. The controller can delay the transition  $4 \to 1$  for as long as the enlarged guard has not been true for longer than  $\Delta$  time units. Formally, using the semantics definition, we know that the controller can wait t time units if  $\mathsf{TS}(v+t,v+t\in[3-\Delta,3+\Delta]) \le \Delta$ , which is equivalent to  $v+t\le 3$ .

- (12) This is the same as (9), but for location 4.

# 3.5 Almost ASAP Semantics Analysis

We have defined the Almost ASAP Semantics formally and given some intuitions and examples about why it is useful to ensure implementability. However, as stated previously, the AASAP semantics is not known to model-checking tools and thus cannot be analyzed "as is". To work around this difficulty, it is shown in [DDR05b] how to construct a timed automaton with a Classical Semantics that is simulable by the Almost ASAP semantics of another automaton which can be constructed effectively. This is formalized by the following theorem:

**Theorem 2** For any Elastic controller A, for any  $\Delta \in \mathbb{Q}^{>0}$ , we can construct effectively a timed automaton  $\mathcal{A}^{\Delta} = \mathcal{F}(A, \Delta)$  such that  $[\![A]\!]_{\Delta}^{\mathsf{AAsap}} \sqsubseteq [\![\mathcal{A}^{\Delta}]\!]$  and  $[\![\mathcal{A}^{\Delta}]\!] \sqsubseteq [\![A]\!]_{\Delta}^{\mathsf{AAsap}}$ .

The interested reader will find all the details of this construction, with full proofs, in [DDR05b].

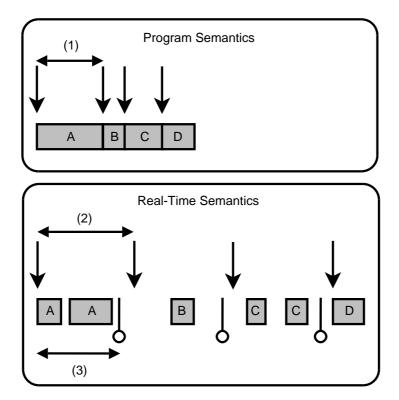

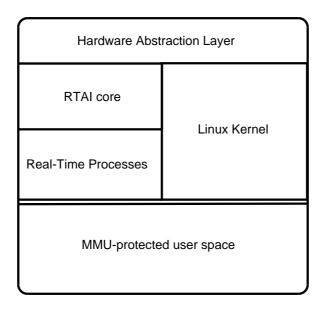

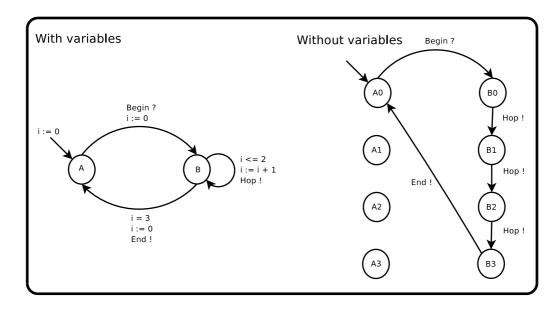

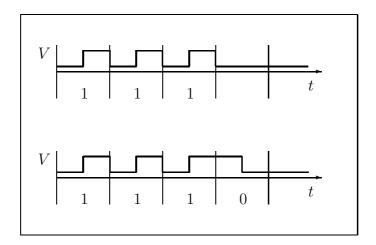

Thanks to this theorem, we are able to analyze the Almost ASAP Semantics effectively. We explain briefly how this is achieved in practice. Suppose we want to control an environment E to avoid some bad region B, subset of the state space of the STTS  $[\![E]\!]$ . Using the methods introduced in the previous chapter, it is possible to design an elastic controller A and verify formally that  $[\![A]\!]$  is safe<sup>1</sup> and controls E to avoid B. Now we want to to know if the control strategy A is implementable. To achieve this, we need to find if there exists some  $\Delta > 0$  such that  $[\![A]\!]_{\Delta}^{\mathsf{AAsap}}$  controls  $[\![E]\!]$  to avoid B as well. Hence, we construct the timed automaton  $\mathcal{A}^{\Delta}$  and analyze it parametrically to verify if there exists a positive rational  $\Delta$  such that the control strategy A controls its environment E in a safe and implementable manner. This parametric analysis can for example be computed with the help of HYTECH. If no parametric tool is available or if its computation does not terminate, it always possible to obtain an approximation of the best  $\Delta$  by doing a binary search in the range of possible values. This way, the best  $\Delta$  value can be approximated up to any precision.